## THE CONTROL SYSTEM FOR INDUCTION ACCELERATION IN THE KEK DIGITAL ACCELERATOR

Taro Sano, Koh-ichi Mochiki, Tokyo City University, Tokyo, Japan Ken Takayama, Taiki Iwashita,

High Energy Accelerator Research Organization (KEK), Ibaraki, Japan

## Introduction

A digital accelerator (DA) is a low energy version of the induction synchrotron which has been demonstrated using the KEK 12 GeV-PS in 2006. The DA is injector-free and its acceleration and bunch confinement are independently carried out by induction cells, which are 1-to-1 transformers driven by individual switching power supplies employing high power and fast semiconductor switching devices (MOS-FET). These devices allows us to realize a so-called all-ion accelerator. A full digital control system of the KEK-DA is under development. It consists of an FPGA and a communication interface to produce current signals for induction cells to accelerate beam ions according to the trigger signal from a bunch menitor.

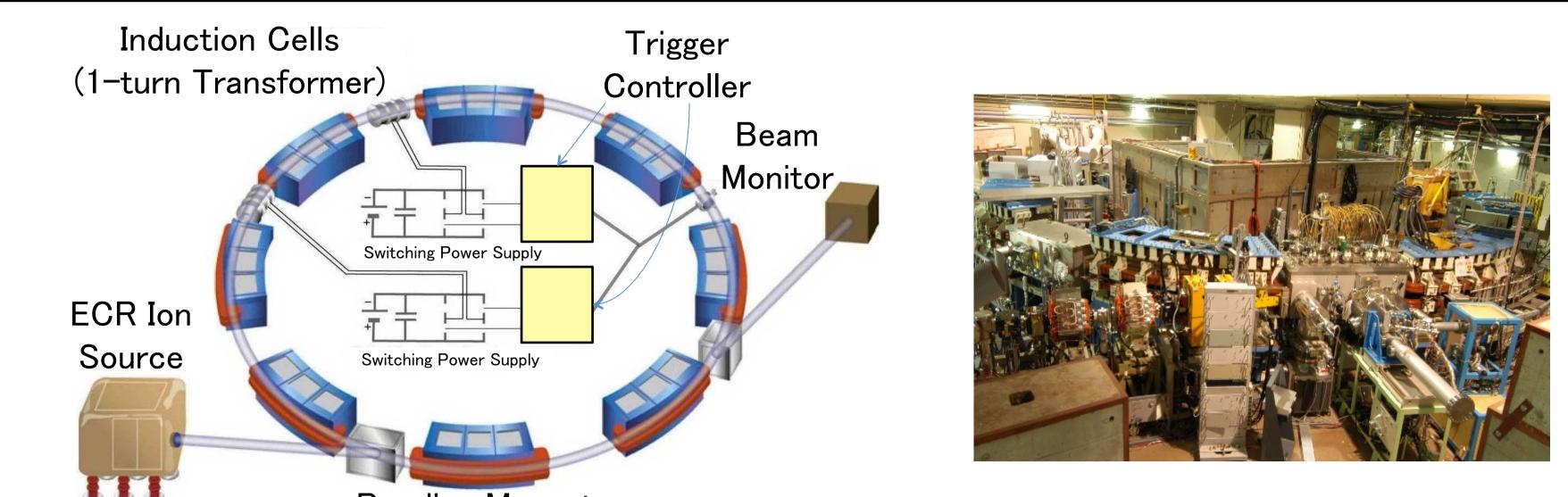

The outline of KEK-DA

KEK-DA

## Present control system

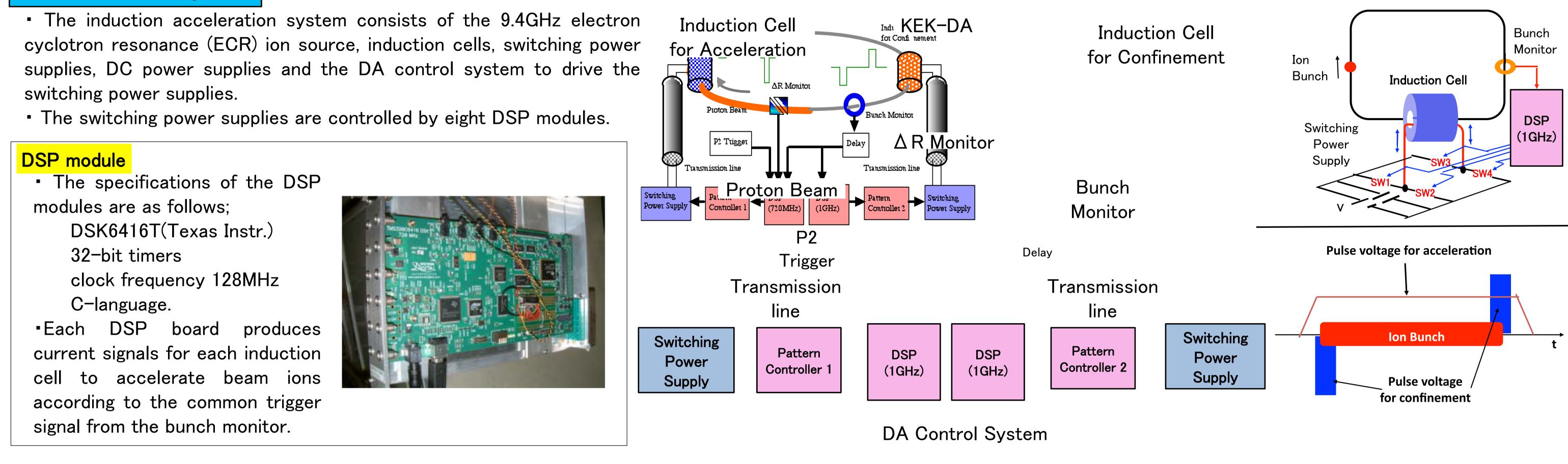

The block diagram of the present control system

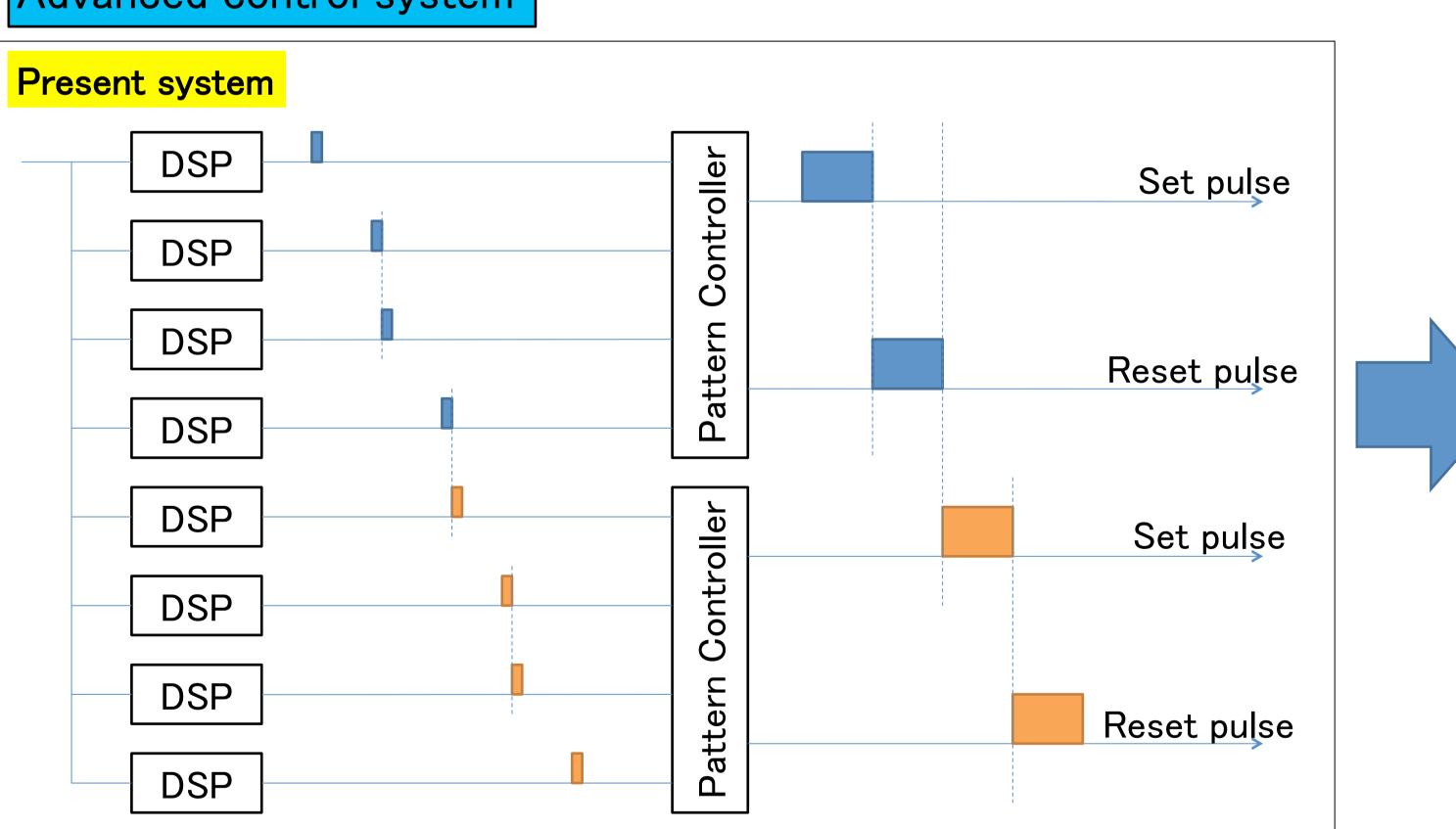

- The present control system is easy to change the software program to modify the control method.

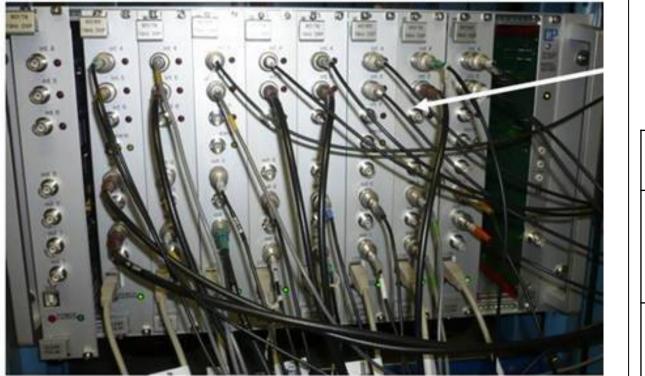

- The eight DSP modules and PCs are large enough to a 19 inch rack.

- In the present system the eight DSPs are executing same program individually loaded by a computer

The block diagram of full digital control system

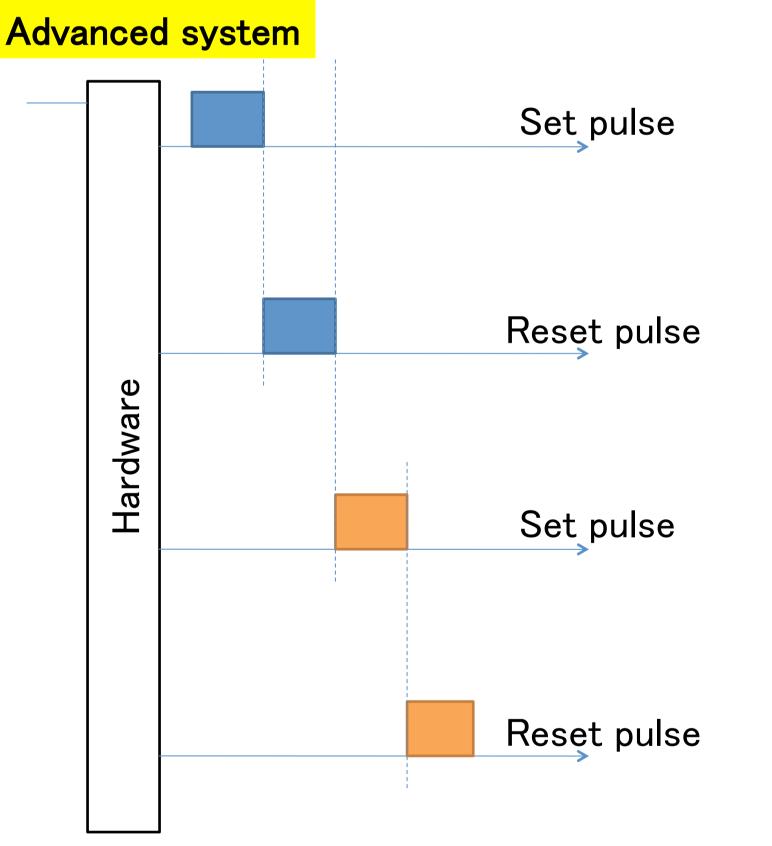

- The FPGA produces four digital signals

for induction cells.

- The system becomes very compact

Its processing time will be improved by parallel processing and arithmetical computation technique using lookup table memories.

- The single FPGA simplifies the hardware circuit and it is very effective to scale down the control system and easy to change the operating parameters.

- The DSP modules can not communicate each other.

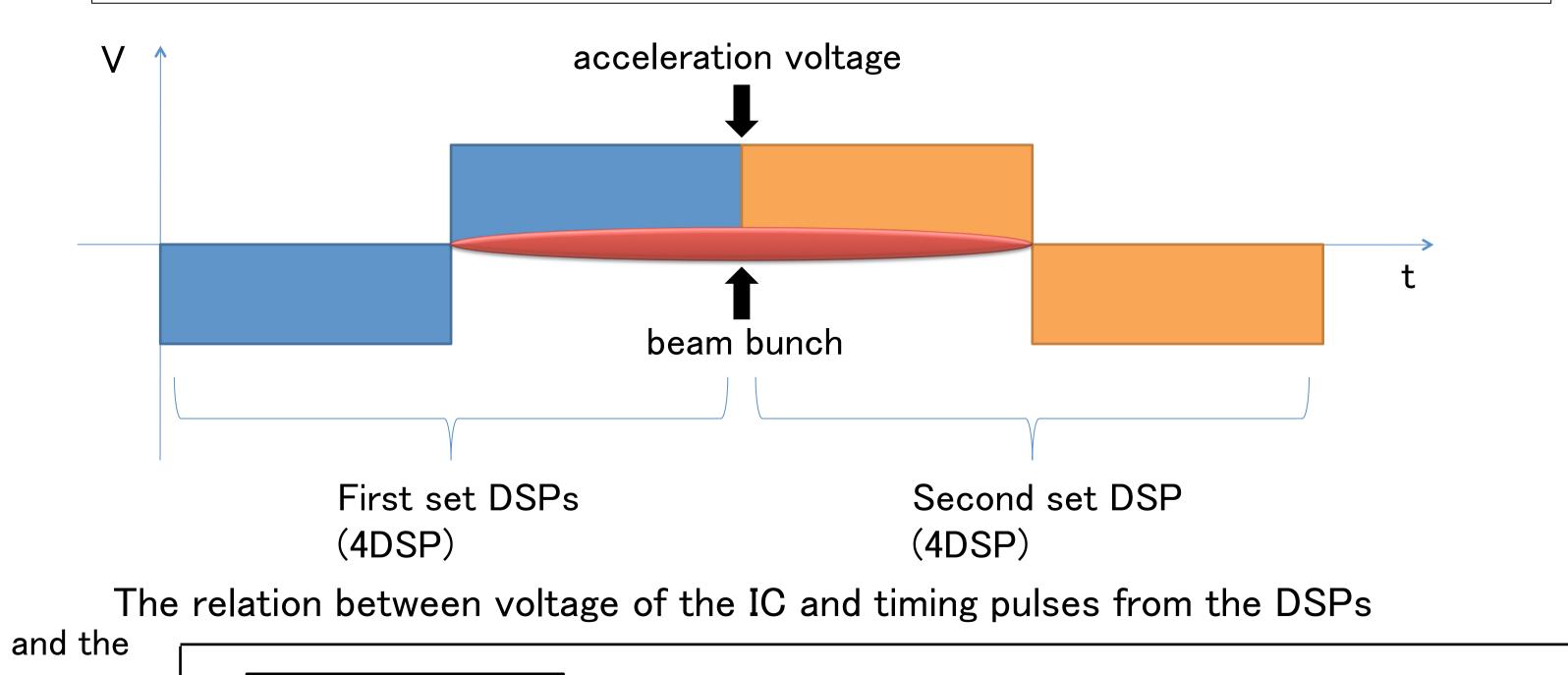

- To realize variable acceleration pulse lengths, start/stop timing of acceleration voltage must be intelligently controlled turn by turn.

- The first pair of induction voltage (blue signals) is for the first cell and the second pair (orange signals) is for the second cell.

8 DSP modules

The merits and demerits of the present system and the advanced system

|                    | Merits                                                                           | Demerits                                |

|--------------------|----------------------------------------------------------------------------------|-----------------------------------------|

| Present<br>system  | <ul> <li>Easy to change<br/>program</li> </ul>                                   | • Over spec                             |

| Advanced<br>system | <ul> <li>Speed up</li> <li>Compact</li> <li>Saving</li> <li>resources</li> </ul> | <ul> <li>Need hardware skill</li> </ul> |

## Future Plan

- To select an evaluation board implemented by an appropriate Xilinx FPGA device and install Verilog HDL program developed by ISE foundation.

- To make simulation test using a pulse generator.

- To compare the performance with the present system.