# Oak Ridge National Laboratory Neutron Sciences Research Accelerator Division

## WEP039: Timing System Upgrade for SNS

David H Thompson, Joze Dedic, Douglas E Curry

#### Abstract

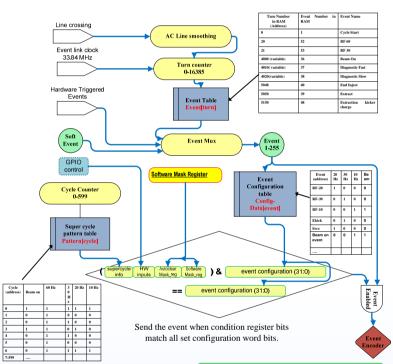

A timing system is a crucial subsystem of every accelerator, responsible for orchestrating the entire machine cycle by cycle. The current SNS timing system is based on the modified BNL solution which in turn is based on previous systems at other sites. The timing master is a collection of low functionality VME building blocks that are highly dependent on creative software to achieve the needed system functionality. The implementation technology of the whole system is backdated, making it impossible to build and maintain spares and boards for machine upgrades. At SNS we chose a roadmap which would allow a gradual upgrade of the timing system without having to redesign everything at once and yet provide a path for future modernization of the infrastructure. This paper presents progress on new timing master and receiver card, which will provide us with more flexible control and greater reliability by tremendously reducing the component count while still retaining compatibility with existing timing receiver units. The designs emphasize the use of FPGA technology in a way that simplifies the supporting software. The design of the system is a collaboration effort of ORNL and Cosylab.

### A New Timing Master

| Feature                         | Old                                                                                                                                                                                                                    | New                                                                                                        |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Generation of fixed events      | Gate cards triggering an event encoder.<br>Events constantly have to be re-timed.<br>Not expandable without adding<br>hardware.                                                                                        | Table driven with a memory<br>location corresponding to a<br>position in the event link time line          |

| Event collision control         | Protects cycle start but not the extract<br>event. MPS events jostle fixed events.                                                                                                                                     | Only one event for every 16 bit<br>clock times. Fixed events are<br>selected first.                        |

| Super Cycle Pattern (Run time)  | Generation of non 60 Hz events require participation by software                                                                                                                                                       | Implemented entirely in hardware.                                                                          |

| RTDL Generator                  | Spans multiple cards, needs pre-loaded<br>map table, not expandable without<br>adding hardware                                                                                                                         | Single memory mapped array that includes per frame enable bits.                                            |

| Generation of RTDL Data         | All done in software including message CRC.                                                                                                                                                                            | Hardware maintains time stamp<br>and other critical RTDL data<br>even when the software is not<br>running. |

| System Hardware<br>Requirements | 1 CPU board, 1 Event encoder using 3 boards, 4 timing delay gates, 1 RTDL encoder using 5 boards, a GPS board, a frequency counter, a fan out module, a utility module, and a set of bus extenders for two VME crates. | 1 CPU Board, 1 timing master<br>board, and one GPS board.                                                  |

The SNS is working toward a 95% beam availability goal during scheduled operation. Historically, timing master outages have been software related and no different than any other IOC. By keeping the machine running without software help, timing master outages are limited to minutes not hours.

#### Hardware Pattern Generator

### AUTO RTDL FRAMES

A few SNS RTDL frames are needed at all times. The hardware provides them when the IOC is down.

- > 001 time stamp / secs(31:8)

- // HW generated timestamp

002 time stamp / nsecs(7:0) + status(7:0) + secs(7:0)

HW generated timestamp + mid-frame status

003 time stamp / nsecs(31:8)

- // HW generated timestamp

➤ 004 HW measured ring revolution period

- // based on measured clock period ➤ 015, 017, 035 0x00000000

- //Includes beam flavor

024 VETO\_NO\_BEAM

025 super-cycle number

#### A New Timing Receiver

Schematic development is under way at ORNL. The FPGA code design will leverage several existing designs. For the event link clock data recovery function an ADN 2816 chip is a proven performer. After testing prototypes we will build 25 modules for installation in selected locations. Phase in of this receiver will occur as replacements and installations are needed.